# **LUMISTAR**

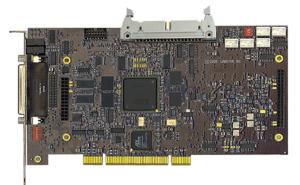

# LS-55-DD PCI Dual Multi-function PCM Decommutator Data Sheet

# **Description:**

The Lumistar LS-55-DD PCI Dual Multi-function PCM Decommutator offers two multifunction

decoms and two optional bit synchronizers (LS-45) in a single PCI card slot. The multi-function decoms are implemented in FPGA using a next generation design based on the LS-50-P. The simulators, decommutators, time code reader and time code generator are achieved on the main board and the bit synchronizer is achieved through a low-profile daughterboard. CVSD voice, h.261 video, and IRIG Chapter 8 decoding are achieved through software.

The IRIG Time Code Reader and Generator operate with IRIG A, B, or G time codes. The Time Code Reader is typically used to insert time information into the PCM minor frame block of data. The Time Code Generator creates and outputs time information in accordance with the IRIG Time Code Standards. Both reader and generator are capable of operating at <sup>1</sup>/<sub>2</sub>, 1, and 2 times the normal rate.

The dual decoms can be used for extremely large formats (65,536 words per minor frame up to 1,024 frames deep) and contains dual ping-pong data output buffers with up to 128K bytes of memory. The second decom can be used for an independent PCM data stream or an embedded data stream in accordance with the IRIG-106 Standard.

The dual PCM simulator generates common, unique, and waveform pattern data words or pseudo-random test pattern (11 through 25 bit) to allow bit error loop calculations to be performed. The two simulators can be used to generate complex data streams with embedded PCM data, or two totally independent data streams. Five-pole Butterworth pre-modulation filtering is provided with 8 selectable data rates on each simulator from 100 Kbps to 20 Mbps.

Key Features: Dual PCI Multifunction PCM Decommutator contains

- 2 PCM Simulators with pre-mod filtering and BERT generating capability

- 2 PCM Decommutators with BERT reading capability

- IRIG Time Code Reader and IRIG Time Code Generator

- LS-40/45-DB Bit Synchronizer Daughterboard Optional (10, 20, 25 Mbps)

- CVSD Voice, h.261 Video, and IRIG Chapter 8 Decoding through LDPS-Pro Software

- Short PCI Board only 7.55 inches long

## **SPECIFICATIONS:**

#### **PCM DECOMMUTATORS (2):**

Input Data Rate Input Signals Input Levels Word Length (VWL)

CRC checker Minor Frame Length Major Frame Length

Bit Order

Frame Sync Pattern

Frame Sync Location Frame Sync Strategy

Sync Error Tolerance Sync Slip Window Data Polarity Subframe Sync

URC Location

SFID Location

#### 64 bps to 30 Mbps NRZ-L data & 0 degree clock Single-ended TTL & RS-422 Variable from 3 to 16 bits per word on a word-by-word basis CRC16/CCITT 2 to 65,536 words per minor frame Up to 1024 minor frames per major frame MSB or LSB-first (word-by-word basis) Up to 64 bits (any pattern with don't care bits (X) may be used) Beginning or end of the frame Adaptive mode (search-lock-verify) & burst mode (search-lock) 0 to 15 bits (selectable) 1, 3, 5, or 7 bits wide (selectable) Normal, inverted or automatic FCC (FAC), SFID or URC (Optional) Any 64 bit window within the first minor frame not including the last bit in the minor frame Any series of contiguous bits not including the last bit in the minor

#### **IRIG A/B/G READER/GENERATOR (1)**:

| Time Reader Input Format | IRIG A, B, or G                           |

|--------------------------|-------------------------------------------|

| Time Reader Rate         | $\frac{1}{2}$ , 1, or 2 times normal rate |

| Input signal level       | 1V p-p nominal                            |

| Latency                  | 2µsec (maximum)                           |

| Data Outputs             | Automatic time tags for PCM data          |

|                          | blocks (time accessible in register       |

|                          | space)                                    |

| Time Generator Output    | IRIG A, B, or G                           |

| Time Generator Rate      | $\frac{1}{2}$ , 1, or 2 times normal rate |

frame

#### **MECHANICAL:**

PCI PCI Board 7.55" Long Daughterboard Form Factor LS-40/45-DB for Bit Synchronizer

#### **POWER REQUIREMENTS:**

| 5V    | 850 ma |

|-------|--------|

| -12 V | 120 ma |

| +12V  | 30 ma  |

### **PCM SIMULATORS (2):**

| Outputs                  | Data, 0 degree clock & minor frame strobes                 |

|--------------------------|------------------------------------------------------------|

| Output Levels TTL, 422   | Single-ended TTL or RS-422 levels<br>on PCM Data and Clock |

| Base-band Output         | 200 mV to 8 V p-p adjustable                               |

| Base-band Pre-mod Filter | 8 on each simulator                                        |

|                          | Selectable; 5-pole Butterworth                             |

| Output Data Rate         | 64 bps to 30 Mbps (NRZ codes)                              |

| Sulput Duin Tuite        | 64 bps to 15 Mbps (all other codes)                        |

| PCM Codes                | NRZ-L/M/S, BI¢-L/M/S                                       |

|                          | DM-M/S, RNRZ-L (2 <sup>11</sup> -1, 2 <sup>15</sup> -1)    |

| Word Length (VWL)        | Variable from 3 to 16 bits per word                        |

| ( ) of a Dongar ( ) ( D) | on a word-by-word basis                                    |

| CRC Generator            | CRC16/CCITT                                                |

| Minor Frame Length       | 2 to 16,383 words per minor frame                          |

| Major Frame Length       | Up to 1024 minor frames per major                          |

| Major France Dengar      | frame                                                      |

| Bit Order                | MSB or LSB-first on a word-by-                             |

|                          | word basis                                                 |

| Frame Sync Pattern       | Fully programmable                                         |

| Sub-Frame Sync           | Fully Programmable                                         |

| Common Words             | May be a single value or selected                          |

|                          | from a group of one minor frame or                         |

|                          | 2048 words whichever is less.                              |

| Unique Words             | Seven may be programmed in any                             |

| 1                        | mainframe, super-commutated, or                            |

|                          | subcommutated channel.                                     |

| Waveform Words           | Five may be programmed to appear                           |

|                          | in every frame at the same location.                       |

|                          | •                                                          |

#### **BERT** (1):

| Pseudo-random patterns |

|------------------------|

| Bit Error Rate         |

| Error Count            |

| Forced Error Modes     |

|                        |

History Log

#### **ENVIRONMENTAL:**

| Temperature (Operating) | 10 to 50 °C                         |

|-------------------------|-------------------------------------|

| Temperature (Non-Op)    | -25 to +70 °C                       |

| Humidity (Operating)    | 10% to 90% Non-Condensing           |

| Humidity (Non-Op)       | Packaging must prevent contact with |

|                         | moisture and contaminants           |

| Special Handling        | Standard ESD methods required       |

Yes

11, 15, 17, 19, 21, 23, and 25

Indicated on Software Indicated on Software

Continuous Forced Error

Single Bit Forced Error